|

为了让读者了解硬件建模的方法,我们选择《文章:域控制器硬件架构 》中的硬件模型,采用建模工具EA和建模语言Sys ML进行了硬件建模。希望能给系统工程师和硬件工程师提供采用Sys ML和建模工具EA进行硬件建模的参考。

注:本文的内容参考了《文章:域控制器硬件架构 》,根据建模需要进行了重新编辑。

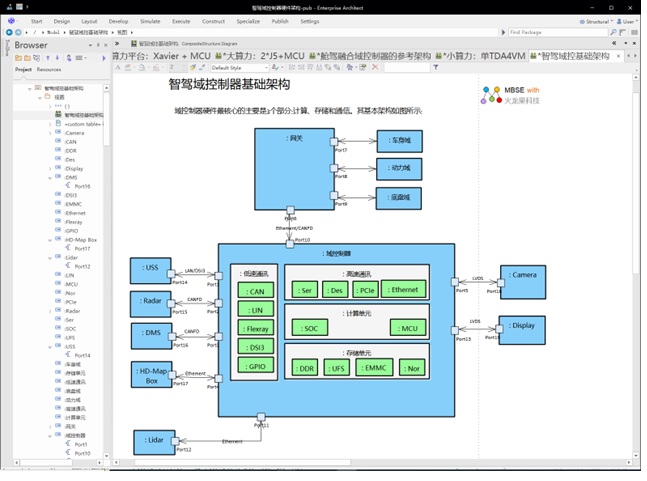

域控制器基础架构

域控制器虽然比较复杂,但是其硬件最核心的主要是3个部分:计算、存储和通信。其基本架构如下所示:

计算单元的硬件主要包括:

• SoC 一般主要负责感知、全局路径规划等,

• MCU 则负责实时性要求很高的整车控制任务。

通信模块的硬件包括:域控制器对外通信,以及控制器内部的片间通信。

对外通信的接口和通信对象,主要包括:

• LVDS :摄像头、屏幕等;

• Ethernet :激光雷达、区域控制器、 T-Box 等;

• CAN :毫米波雷达、超声波雷达控制器、 EPS 、 ESP 、 VCU 等;

• LIN :超声波雷达采用 LIN 总线就够了;

• FlexRay :部分特定控制器;

• RS232 :导航定位等;

• A2B :麦克风、音响、部分传感器等;

控制器内部的片间通信主要包括: SPI 、 I2C 、 PCIe 、 NVLink 等。

存储部分主要包括 RAM 、 eMMC 、 Nor Flash 、 UFS 等。

除了上述三个核心模块之外,域控制器硬件还包括电源 PMIC 、信息安全芯片、阻容感被动器件、散热组件、外壳、接插件、 PCB 板等。

根据所能实现功能的不同,域控制器的硬件构成差别巨大,其硬件成本可能从数千元到数万元不等。

通常根据算力的不同,域控制器可以分为三类:

• 小算力平台:也被称为轻量级行泊一体域控制器,可实现基本的 L2 功能;

• 中算力平台:可实现高速 NOA ;

• 大算力平台:可实现城市 NOA 。

下面逐一介绍。

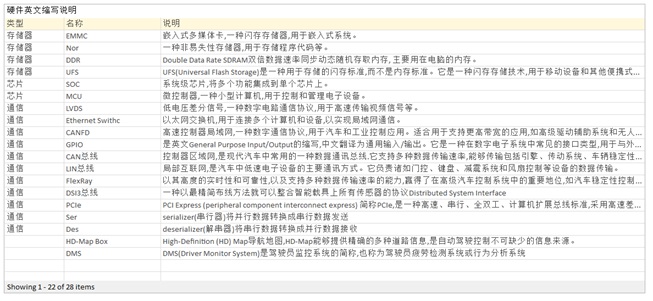

小算力平台:

如下是小算力平台的典型硬件方案:

• 硬件包括: TDA4VM/TDA4VM Eco 、 MCU 以及对外接口和外接传感器。

• 支持的传感器: 5~6Camera , 3~5Radar ;

• 实现的功能: 基本 L2 行泊一体功能。例如 TJA ( 交通拥堵辅助 )、 HWA ( 高速辅助驾驶 )、 APA ( 自动泊车辅助 )等。

如下是 小算力硬件平台的硬件结构图例:

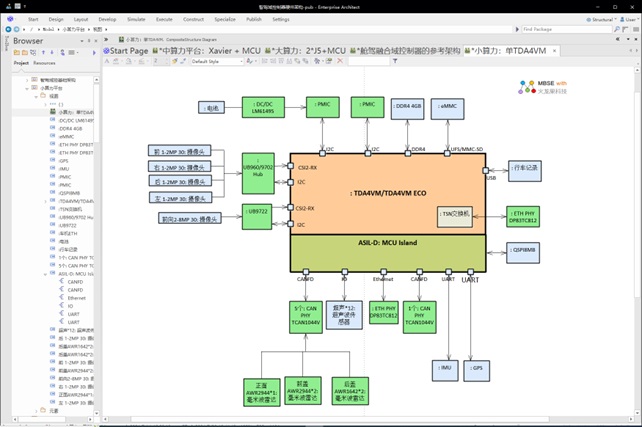

中算力平台: Xavier + MCU

中算力平台的典型硬件方案如下:

• 硬件包括; Xavier + MCU 。

• 支持传感器: 10~11Camera , 3~5Radar ;

• 实现功能:高级 L2 行泊一体,如高速 NOA (导航辅助驾驶) , 记忆行车,记忆泊车等。

如下是 中算力硬件平台的硬件结构图例:

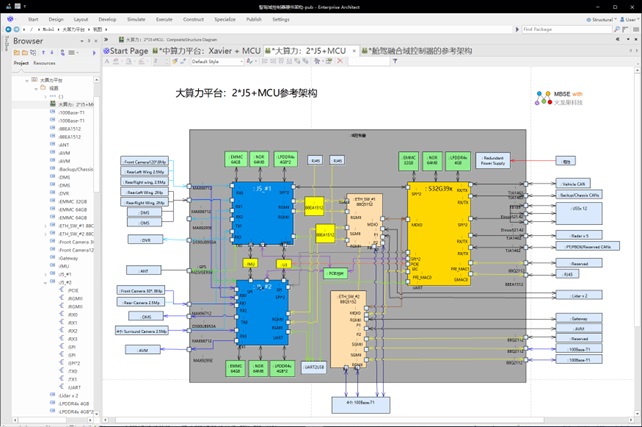

大算力平台: 2*J5+MCU

大算力平台的典型硬件方案如下:

• 硬件包括: 2*J5+MCU 。

• 支持传感器: 10~13Camera , 1~5Radar ,以及 1~3Lidar ;

• 实现功能: L2~L3 行泊一体, 城市 NOA (导航辅助驾驶), AVP (自主代客泊车)等 .

如下是 中算力硬件平台的硬件结构图例:

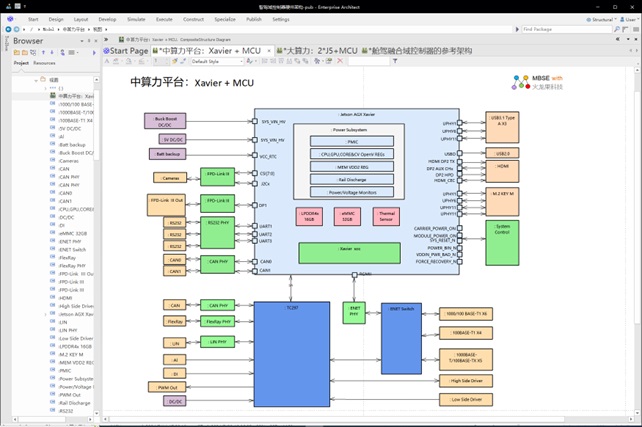

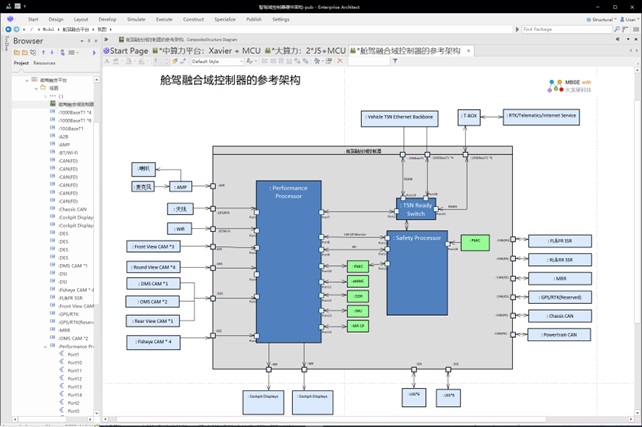

舱驾融合平台

为了提高功能集成和降低通信成本,也演进出了舱驾一体方案,也就是把座舱域和智驾域的功能集成在一个高性能计算单元内,实现座舱域与智驾域的融合。

舱驾一体的主要优势在于:

• 降低成本:物料方面,相比于多 SoC 方案,单芯片集成度更高、使用物料更少,且共用一套散热系统带来散热成本下降;

• 降低通讯延时,优化功能体验:使舱和驾之间数据传输从板间通讯变为片内通讯并共享内存;

• 优化算力利用率:当前芯片还未做到完全的算力动态分配,但未来会从静态配置的算力迭代至动态分布的算力;

• 应用层面创新空间更大:舱驾融合后,有助于工程师在整体维度进行功能开发,相互调度各自服务或资源,从而融合出更有创新性的应用;

舱驾融合域控制器的参考架构如下:

• 硬件包括:

1) Performance Processor :负责大数据量的密集计算。

2) Safety Processor :负责国内安全的处理,例如 诊断,功能安全。

3) TSN Ready Switch :负责网络通信。

4) 外接传感器 ;包括设想图、激光雷达、毫米波雷达等等。

• 功能: 在一个高性能计算单元内,实现座舱域与智驾域的融合,可同时支持智舱和智驾功能。

了解智驾域控制器的详细信息,请浏览 《 硬件模型:智驾域控制器(基于建模工具EA)》 |  20 次

20 次